# A text book on

Useful for IAS, IES, GATE, PSUs and other competitive examinations

# A. RAJKUMAR

M. Tech. (JNTU Kakinada) (Ph.D) JNTU Hyderabad Expert Faculty, MADE EASY

Corporate Office: 44-A/4, Kalu Sarai, New Delhi-16 Website: www.madeeasypublications.org | Phone: 011-45124660, 08860378007

### **MADE EASY Publications**

Corporate Office: 44-A/4, Kalu Sarai, New Delhi-110016 Website: www.madeeasypublications.org I Phone: 9021300500 E-mail: infomep@madeeasy.in

### A text book on Analog Circuits

© Copyright, by MADE EASY Publications.

All rights are reserved. No part of this publication may be reproduced, stored in or introduced into a retrieval system, or transmitted in any form or by any means (electronic, mechanical, photocopying, recording or otherwise), without the prior written permission of the above mentioned publisher of this book.

First Edition: 2012 Reprint: 2013 Reprint: 2014 Reprint: 2015 Reprint: 2019 **Reprint: 2022**

Typeset at: MADE EASY Publications, New Delhi-110016

Dedicated to

My Wife

# A. Smitha

who believes, in

The best teacher teaches from the heart, ....not from the book....

## PREFACE

I have great pleasure in writing the book of core subject of Electronics Engineering viz. **Analog Circuits.** A thorough understanding of the concepts developed in this book will prepare the reader for more advanced course on the subject. The entire syllabus of Analog circuits is presented in a simple and lucid style to make it comprehensible to an average student. This text book has been written to meet the requirements for the students of B.E./B.Tech., ECE, EEE, EIE.

In this book, I have tried to present the approach for competitive examinations like GATE, IES and IAS. While teaching various categories of students, I understood that, it becomes very easy for the students when things are explained by going through the fundamentals. So in the present book, I tried to explain most of the topics through the basics. The **Questions with Solutions** which already appeared in competitive examinations like GATE, IES are incorporated in each chapter.

First, I would like to thank **Mr. B. Singh** (Chief Managing Director, MADE EASY Group) for giving me the opportunity for writing the text book. His constructive suggestions and support helped me a lot.

I express my heartfelt regard and gratitude to my teacher Dr. Srinivas Rao from whom I have learnt the subject matter and which gave me inspiration to write this book.

I would also like to thank my H.O.D. Dr. Koteswara Rao and Principal Dr. Chinna Keshava Rao (CBIT), Mr. Sudarshan Reddy (Associate Prof. in CBIT) who always inspire me in discipline and hard work.

A special thanks to Mr. Sai Prasad who always, encourages me and gave me the first opportunity to teach for competitive exams.

I express my sincere gratitude to my favorite Sir, Mr. Prem R. Chadha, friends M.V. Kiran Kumar, Ramana Reddy, Krishna Kumar, Jagan, Krishna who always direct me in a right path.

Last but not the least, I also thank MADE EASY staff especially Vinod Kumar and Md. Asim who put their sincere efforts to develop this book in time.

Any comments and suggestions for the improvement of this book will be thankfully acknowledged and incorporated in the next edition.

A. Rajkumar

# CONTENTS

# **BJT Biasing and Thermal Stabilization**

- 1.1 Operating Point and DC Load Line 2

- 1.2 Temperature Dependence on Transistor Parameters 5

- 1.3 Stability Factor 6

- 1.4 Biasing Techniques 7

- 1.5 Fixed Bias Circuit 7

- 1.6 Collector to Base Bias 8

- 1.7 Voltage Divider Bias or Self Bias 10

- 1.8 Bias Compensation by Diode 12

- 1.9 Bias Compensation by Thermistor 12

- 1.10 Bias Compensation by Sensistor 12

- 1.11 Thermal Run away 13

# **Small Signal Analysis of BJT**

### Low Frequency Analysis

- 2.1 Introduction 32

- 2.2 Two Port Network 32

- 2.3 Hybrid Model of BJT 34

- 2.4 Hybrid Model in Different Configurations 34

- 2.5 Typical Values of H-Parameters 35

- 2.6 Conversion Formulas of H Parameters in Different Configuration 35

- 2.7 Transistor Amplifier Analysis Using Exact Model 35

- 2.8 Transistor Amplifier Analysis Using Approximate Model 38

### **High Frequency Analysis**

- 2.9 Introduction 41

- 2.10 Hybrid- $\pi$  Model **41**

- 2.11 Typical Values of Hybrid- $\pi$  Parameters 42

- 2.12 Expressions for Hybrid- $\pi$  Parameters 43

- 2.13 Variation of Hybrid  $\pi$  Parameters With I<sub>c</sub>, V<sub>CE</sub> and Temperature **48**

- 2.14 Common Emitter Short Circuit Current Gain 48

- 2.15 High Frequency Current Gain with Resistive Load 50

### **Frequency Response of an Amplifier**

- 2.16 Low Frequency Range 52

- 2.17 High Frequency Range 52

- 2.18 Midband Range 52

- 2.19 Application of Bodeplot in Frequency Response of Amplifier 53

# **Feedback Amplifiers**

- 3.1 Introduction 66

- 3.2 Limitations of Basic Amplifier 66

- 3.3 Feedback Principle 66

- 3.4 Classification of Amplifiers 67

- 3.5 General Theory of Feedback 69

- 3.6 Concept of Positive Feedback and Negative Feedback 71

- 3.7 Advantages of Negative Feedback Amplifiers 72

- 3.8 Topologies of Feedback 76

- 3.9 Voltage Series Feedback 79

- 3.10 Voltage Shunt Feedback 79

- 3.11 Current Series Feedback 81

- 3.12 Current Shunt Feedback 82

- 3.13 Method of Analysis of a Feedback Amplifier 83

# Oscillators

- 4.1 Introduction 96

- 4.2 Types of Oscillators 96

- 4.3 Essentials of Transistor Oscillator 97

- 4.4 Barkhausen Criterion 98

- 4.5 RC Phase Shift Oscillator 99

- 4.6 Wien Bridge Oscillator 103

- 4.7 Comparison of RC Oscillators 105

- 4.8 LC Oscillators 106

- 4.9 Hartley Oscillator 107

- 4.10 Colpitts Oscillator 109

- 4.11 Clapp Oscillator 111

- 4.12 Crystal Oscillator 112

# **Power Amplifiers**

- 5.1 Introduction 124

- 5.2 Difference Between Voltage Amplifier and Power Amplifier 124

- 5.3 Power Amplifiers 126

- 5.4 Power Amplifier Classes 126

- 5.5 Comparison of Amplifier Classes **128**

- 5.6 Class-A Power Amplifier **128**

- 5.7 Distortion in Amplifiers **133**

- 5.8 Class-B Power Amplifier 134

- 5.9 Class-B Push Pull Amplifier 136

- 5.10 Complementary Symmetry Class-B Amplifier 140

- 5.11 Comparison Between Push Pull and Complementary Symmetry 140

- 5.12 Cross Over Distortion 141

- 5.13 Class-AB Amplifier 141

- 5.14 Safe Operating Area (SOA) For a Transistor 142

- 5.15 Thermal Analogy of Power Transistors 143

- 5.16 Class-C Power Amplifier 144

- 5.17 Class-D Amplifiers 145

- 5.18 Class-S Power Amplifier 146

# **Multistage Amplifiers**

- 6.1 Introduction 154

- 6.2 Characteristics of Cascaded Amplifier 154

- 6.3 Gain in Decibels 155

- 6.4 Selection of an Amplifier Configuration For Cascade Connection 156

- 6.5 Methods of Coupling in Multistage Amplifiers 156

- 6.6 RC Coupled Amplifiers 157

- 6.7 Transformer Coupled Amplifier 158

- 6.8 Direct Coupled Amplifiers 160

- 6.9 Comparison of Different Coupling Techniques 161

- 6.10 Rise Time-bandwidth Relation 161

- 6.11 Cascode Amplifier (CE-CB) 163

- 6.12 Darlington Pair (CC-CC) 163

- 6.13 Bootstrap Emitter Follower 164

- 6.14 Millers Theorem 165

- 6.15 Effect of Cascading on Bandwidth (identical stages) 166

- 6.16 Effect of Cascading on Bandwidth (non identical stages) 168

# Linear and Non Linear Wave Shaping

### Linear Wave Shaping

- 7.1 Introduction 176

- 7.2 High Pass RC Circuit 176

- 7.3 RC Differentiator 177

- 7.4 Sinusoidal Input 178

- 7.5 Response of Step, Pulse, Square, Ramp, Exp. for High Pass ckt 179

- 7.6 Low Pass RC Circuit 180

- 7.7 Low Pass RC Circuit as Integrator 181

- 7.8 Sinusoidal Input 181

- 7.9 Response of Step, Pulse, Square, Ramp and Exp. for Low Pass ckt 183

### Non Linear Wave Shaping

- 7.10 Clippers 184

- 7.11 Shunt Clipper Models 184

- 7.12 Series Clipper Models 189

- 7.13 Clipping at Two Independent Levels 195

- 7.14 Clamping Circuits 199

# **Rectifiers, Filters and Voltage Regulators**

### Rectifiers

- 8.1 Introduction **216**

- 8.2 Rectifier Parameters 216

- 8.3 Half Wave Rectifier 217

- 8.4 Full Wave Rectifier 222

- 8.5 Bridge Rectifier 226

### Filters

- 8.6 Introduction 227

- 8.7 Capacitor Filter 228

- 8.8 Inductor Filter 231

- 8.9 L Section Filter 234

- 8.10  $\pi$  Section Filter **235**

- 8.11 Bleeder Resistor 236

### **Voltage Regulators**

- 8.12 Introduction 236

- 8.13 Block Diagram of Power Supply 236

- 8.14 Load Regulation 237

- 8.15 Line Regulation 237

- 8.16 Series Voltage Regulator 237

- 8.17 Shunt Voltage Regulator 238

- 8.18 Limitations of Series and Shunt Voltage Regulators 238

# **Operational Amplifiers**

### **Differential Amplifiers**

- 9.1 Introduction 248

- 9.2 Differential Amplifier 248

- 9.3 Circuit Configurations 249

- 9.4 Circuit Diagrams 250

- 9.5 Operating Point (Q) for a Differential Amplifier 252

- 9.6 Practical Design Problems in Differential Amplifiers 253

- 9.7 Swamping Resistor Technique 254

- 9.8 Constant Current Source Circuits 255

- 9.9 Current Mirror Circuits 257

- 9.10 Common-Mode Voltage Gain **260**

- 9.11 Differential Amplifier With Active Load 262

### **Operational Amplifiers**

- 9.12 Block Diagram of Operational Amplifier 263

- 9.13 Symbol Representation of Op-Amp 263

- 9.14 Equivalent Circuit of an Op-Amp **264**

- 9.15 Ideal Voltage Transfer Characteristics 264

- 9.16 Pin Diagram of 741 IC **265**

- 9.17 Op-amp Characteristics 265

- 9.18 Importance of Negative Feedback in Op-Amp 270

- 9.19 Virtual Ground 271

### **Applications of Operational Amplifier**

- 9.20 Inverting Amplifier 271

- 9.21 Non-Inverting Amplifier 272

- 9.22 Phase Shifter 273

- 9.23 Voltage Follower 273

- 9.24 Differential Amplifier 274

- 9.25 Subtracter **275**

- 9.26 Inverting Adder 275

- 9.27 Non Inverting Adder 276

- 9.28 Current to Voltage Converter 277

- 9.29 Voltage to Current Converter 278

- 9.30 Voltage to Current Converter (with load) 278

- 9.31 Op-Amp Integrator 279

- 9.32 Op-Amp Differentiator 280

- 9.33 Precision Rectifiers 281

- 9.34 Current Amplifiers **285**

- 9.35 Instrumentation Amplifier 286

- 9.36 Voltage Limiters 287

- 9.37 Log Amplifiers 289

- 9.38 Anti Log Amplifiers 289

- 9.39 Analog Multiplier 290

- 9.40 Analog Divider 291

- 9.41 Peak Detector **292**

- 9.42 Sample and Hold Circuit 292

- 9.43 Op-amp Comparator 293

- 9.44 Schmitt Trigger 295

- 9.45 Astable Multivibrator (free-running oscillator) 297

- 9.46 Triangular-Wave Generator 298

- 9.47 Monostable Multivibrator (pulse generator) 299

### **Active Filters**

- 9.48 Introduction **301**

- 9.49 Classification of Active Filters **301**

- 9.50 Butterworth Filter 303

- 9.51 First Order Low Pass Butterworth Filter 304

- 9.52 First Order High Pass Butterworth Filter 306

- 9.53 Band Pass Filters 309

- 9.54 Band Stop Filter 313

- 9.55 All Pass Filter 315

### 555 Timer

- 9.56 Introduction **318**

- 9.57 555 Timer Pin Configuration 318

- 9.58 Block Diagram of 555 Timer 319

- 9.59 555 Timer as Monostable Multivibrator 320

- 9.60 555 Timer as Astable Multivibrator 323

# 10

# **FET Biasing and Small Signal Analysis**

### **FET Biasing**

- 10.1 Introduction 370

- 10.2 DC-Load Line and Bias Point 370

- 10.3 Fixed Bias Circuit 372

- 10.4 Self Bias 373

- 10.5 Voltage Divider Bias 374

### **Small Signal Analysis**

- 10.6 Introduction 376

- 10.7 Common Source Bypass JFET Amplifier 377

- 10.8 Common Source Unbypass JFET Amplifier 379

- 10.9 Common Drain JFET Amplifier 381

- 10.10 Common Gate JFET Amplifier 382

- 10.11 Comp. Between CS Bypass, CS Unbypass, CD, CG Amplifiers 385

# **Multivibrators and Time Base Generators**

### Multivibrators

- 11.1 Introduction 394

- 11.2 Bistable Multivibrator 395

- 11.3 Schmitt Trigger 397

- 11.4 Mono Stable Multivibrator 399

- 11.5 Astable Multivibrator 401

### **Time Base Generators**

- 11.6 Introduction 404

- 11.7 Sweep Voltage 404

- 11.8 Methods of Generating a Time Base Waveform 405

- 11.9 Exponential Sweep Circuit 406

- 11.10 UJT Sweep Generator 406

- 11.11 Bootstrap Sweep Generator 408

- 11.12 Miller Sweep Circuit 410

# **CHAPTER 1**

# BJT BIASING & THERMAL STABILIZATION

# **About This Chapter**

- Operating point and DC load line.

- AC load line.

- Stability factors S, S' and S".

- Various biasing circuits like fixed bias, collector to base bias and self bias.

- Compensation circuits.

- Thermal run-away and conditions to maintain thermal stability.

# **BJT Biasing &** Thermal Stabilization

# 1.1 Operating Point and DC Load Line

- It is clear that the transistor functions most linearly when it is constrained to operate in its active region.

- To establish an operating point in this region it is necessary to provide appropriate direct potentials and currents, using external sources.

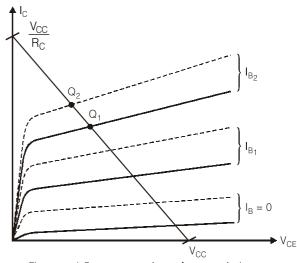

- Once an operating point Q is established as shown below:

# ANALYSIS

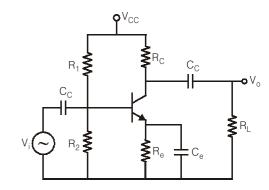

Assume common emitter amplifier circuit In DC analysis,

(i) ac should be grounded

(ii)

$$X_c \propto \frac{1}{f}$$

, as  $f \to 0$ ,  $X_c \to \infty$

:. Capacitor is open.

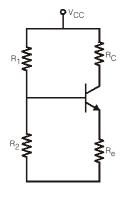

## **DC Equivalent Model**

Figure 1.1 Common emitter amplifier

The output loop equation is given by

$$V_{CC} = I_C (R_C + R_e) + V_{CE}$$

$$I_C = \frac{V_{CC}}{R_C + R_e} - \frac{V_{CE}}{R_C + R_e}$$

Above equation represents like a straight line y = mx + CWhen  $I_{C} = 0$ ,  $(V_{CE})_{max} = V_{CC}$

$$V_{CE} = 0, \quad (I_C)_{max} = \frac{V_{CC}}{R_C + R_e}$$

Slope of DC load line =  $-\frac{1}{R_{C} + R_{e}}$

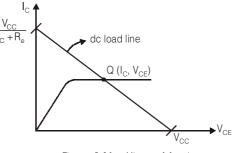

# **Output Characteristics of Common Emitter**

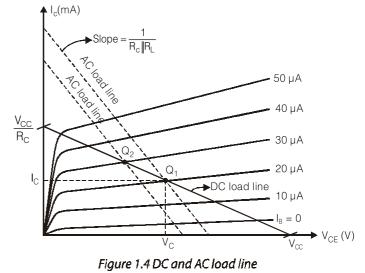

Fig. 1.2 DC load line and Q point

# **Q** Point

"The intersection point between the dc load line and sample graph of I<sub>C</sub> is called as operating point (or) Quiescent point".

# **DC Load Line**

"The locus of all the Q points are concentrated on a line called as DC load line".

- When time varying excursions of the input signal (base current, for example) is applied to common emitter amplifier, should cause an output signal (collector voltage or collector current) of the same wave form.

- If the output signal is not a faithful reproduction of the input signal, for example, if it is clipped on one side. The operating point is unsatisfactory and should be relocated on the collector characteristics.

- The question now naturally arises as, how to choose the operating point.

- Note that even if we are free to choose R<sub>c</sub>, R<sub>L</sub>, R<sub>b</sub> and V<sub>CC</sub>, we may not operate the transistor every where in the active region, because the various transistor ratings limit the range of useful operation.

- These ratings are

(i) (V<sub>CE</sub>)<sub>max</sub>

(ii) (I<sub>C</sub>)<sub>max</sub>

(iii) P<sub>c max</sub>

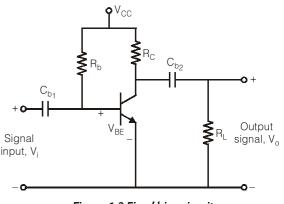

# **Capacitive Coupling**

- The capacitor C<sub>b1</sub> is to couple the input signal to the transistor, as indicated in the Figure (1.3).

- In this diagram, one end of V<sub>i</sub> is at ground potential, and the collector supply V<sub>CC</sub> also provides the biasing base current I<sub>B</sub>.

- Under quiescent conditions (no input signal), C<sub>b1</sub> (called a blocking capacitor) acts as an open circuit because the reactance of a capacitor is infinite at zero frequency (dc).

Figure 1.3 Fixed bias circuit

- The capacitances C<sub>b1</sub> and C<sub>b2</sub> are chosen large enough so that, at the lowest frequency of excitation their reactances are small enough so that they can be considered to be short circuits.

- These coupling capacitors block dc voltages but freely pass signal voltages.

For example, the quiescent collector voltage does not appear at the output, but V<sub>o</sub> is an amplified replica of the input signal V<sub>i</sub>.

- The ac output signal voltage may be applied to the input of another amplifier with out affecting its bias, because of the blocking capacitor C<sub>b2</sub>.

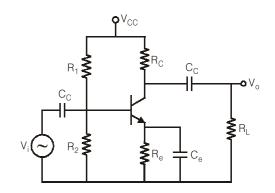

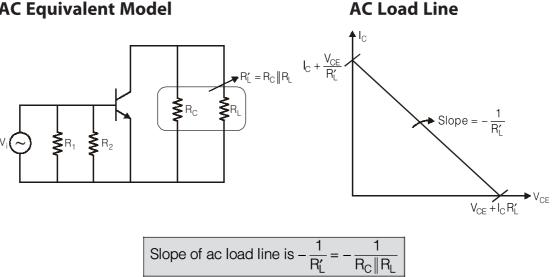

### **DC and AC Load Lines**

- We noted that under dc conditions C<sub>b2</sub> acts as an open circuit. Hence the quiescent collector current and voltage are obtained by drawing a static (dc) load line.

- If  $R_L = \infty$  and if the input signal (base current) is large and symmetrical, we must locate the operating point  $Q_1$ at the centre of the DC load line. In this way the collector voltage and current may vary approximately symmetrically around the quiescent values  $V_C$  and  $I_C$  respectively.

- If  $R_1 \neq \infty$ , however, a dynamic (ac) load line must be drawn.

- Since, we have assumed that, at the signal frequency,  $C_{b2}$  acts as a short circuit, the effective load  $R'_{I}$  at the collector is  $R_{C}$  in parallel with  $R_{L}$ .

## **AC Load Line Analysis**

Assume CE amplifier circuit:

## **AC Analysis**

(i) DC should be grounded.

(ii)

$$X_C \propto \frac{1}{f}$$

, as  $f \to \infty \therefore X_c \to 0$

i.e. capacitor acts as short circuit.

## **AC Equivalent Model**

- We observe that the input signal may swing a maximum of approximately 20  $\mu$ A around Q<sub>1</sub> because, if the base current decreases by more than 20 µA, the transistor is driven off.

- If a larger input swing is available, then in order to avoid cut-off during a part of the cycle. The quiescent point must be located at a higher current.

- Suppose we locate  $Q_2$  on the dc load line such that a line with a slope corresponding to the ac resistance  $R'_L$  and drawn through  $Q_2$  gives as large as output as possible with out too much distortion.

$R_{c} + R_{c}$

The choice of  $Q_2$  allows an input peak current swing of about 30  $\mu$ A.

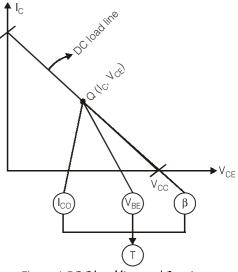

### **1.2 Temperature Dependence on Transistor Parameters**

The sources of instability of I<sub>C</sub> are essentially three:

- (i) Reverse saturation current I<sub>CO</sub>

- (ii) Base-emitter voltage V<sub>BE</sub>

- (iii) Current gain  $\beta$

- I<sub>CO</sub> Versus Temperature "I<sub>CO</sub> increases by 7%/°C rise in temperature". (or)

"I<sub>CO</sub> doubles for every 10°C rise in temperature". i.e. as temperature increases, I<sub>CO</sub> also increases.

V<sub>BE</sub> Versus Temperature

"The base to emitter voltage V<sub>BE</sub>, which decreases at the rate of 2.5 mV/°C for both Ge and Si transistors."

$$\frac{dV_{BE}}{dT} = -2.5 \,\text{mV/°C}$$

i.e. as temperature increases, V<sub>BE</sub> decreases.

- β Versus Temperature

- (a)  $\beta$  increases with temperature

Figure 1.5 DC load line and Q point

- (b) Replacement of Transistor

- We see that the spacing of the output characteristics will increase or decrease as β increases or decreases.

- Though transistors are identified by a type number, but even for a given type, the characteristics differ from piece to piece.

- β is the ratio of collector current I<sub>C</sub> and base current I<sub>b</sub>. As for the same base current, the collector current of the transistor will vary from replacement of the device.

- Generally β is greater for the replacement of transistor.

Figure 1.6 Common emitter characteristics

# 1.3 Stability Factor

"It is a measure of variation in the operating point with respect to the temperature is called as stability factor".

$I_{C}$  is a function of  $I_{CO}$ ,  $V_{BE}$  and  $\beta$ . It is convenient to introduce the three partial derivatives of  $I_{C}$  with respect to these variables. These derivatives are called the stability factors S, S<sup>'</sup> and S<sup>''</sup>.

$$S = \frac{\partial I_{C}}{\partial I_{CO}} \Big|_{V_{BE},\beta \text{ constant}}$$

$$S' = \frac{\partial I_{C}}{\partial V_{BE}} \Big|_{I_{CO},\beta \text{ constant}}$$

$$S'' = \frac{\partial I_{C}}{\partial \beta} \Big|_{I_{CO},V_{BE} \text{ constant}}$$

### **Expression for Stability Factor**

$$I_{C} = \beta I_{b} + (1 + \beta) I_{CO} \quad \text{d.w.r.t } I_{C}$$

$$I = \beta \frac{\partial I_{b}}{\partial I_{c}} + (1 + \beta) \frac{\partial I_{CO}}{\partial I_{C}}$$

$$S = \frac{\partial I_{C}}{\partial I_{CO}} = \frac{1 + \beta}{1 - \beta \frac{\partial I_{b}}{\partial I_{C}}}$$

**Conclusion:**

- Ideally the stability factor should be zero.

- Practically stability factor should be very very less.

$$P_{\rm C} = V_{\rm cc} I_{\rm c} - I_{\rm c}^2 (R_{\rm c} + R_{\rm e})$$

Taking derivative w.r.t. I<sub>C</sub>

$$\frac{\partial P_c}{\partial I_c} = V_{cc} - 2I_c (R_c + R_e)$$

Stability factor S,

$$S = \frac{\partial I_{C}}{\partial I_{CO}} = \frac{\partial I_{C}}{\partial T_{j}} \times \frac{\partial T_{j}}{\partial I_{CO}}$$

We know that  $I_{co}$  increases at the rate of 7% per°C

$$\frac{\partial I_{CO}}{\partial T_{j}} = 0.07 I_{CO}$$

or

$$\frac{\partial T_{j}}{\partial I_{CO}} = \frac{1}{0.07 I_{CO}}$$

$$\frac{\partial I_{C}}{\partial T_{j}} = S \times 0.07 I_{CO}$$

$$\left\{ V_{CC} - 2I_{C} \left( R_{C} + R_{e} \right) \right\} \times S \times 0.07I_{CO} < \frac{1}{\theta}$$

### Conclusion

The following three conditions leads to thermal run-away:

(i)

$$\frac{\partial P_{C}}{\partial T_{j}} < \frac{\partial P_{D}}{\partial T_{j}}$$

(ii)  $\frac{\partial P_{C}}{\partial T_{j}} < \frac{1}{\theta}$

(ii)

$$\left\{ V_{CC} - 2I_{C} \left( R_{C} + R_{e} \right) \right\} \times S \times 0.07 I_{CO} < \frac{1}{\theta}$$

# **SUMMARY**

- The collector current of a transistor varies with I<sub>CO</sub>, β and V<sub>BE</sub> which in turn are dependent on temperature variation.

- × Stability factor S is given by

$$S = \frac{\partial I_{c}}{\partial I_{co}} = \frac{1+\beta}{1-\beta \frac{\partial I_{b}}{\partial I_{c}}}$$

- **\*** Fixed bias circuit is the simplest biasing arrangement and has a stability factor  $S = 1 + \beta$ .

- \* Collector to base bias circuit is an improvement over fixed bias circuit and has a stability factor

$$S = \frac{1+\beta}{1+\beta \frac{R_c}{R_b + R_c}}$$

### **MADE EASY**

\* The self bias circuit consists of three resistors R1, R2, Re, usually. The RE is bypassed with a large value capacitor  $C_E$ . The stability factor,

$$S = \frac{1+\beta}{1+\beta} \frac{R_e}{R_b + R_e}$$

- for obtaining low value of S, it is necessary to choose a low value of  $\frac{R_b}{R_e}$ . Bias compensation can be achieved either by use of diode, thermistor or sensistor. ×.

- Stability factor S' =  $\frac{\partial I_C}{\partial V_{RE}}$  and stability factor S" =  $\frac{\partial I_C}{\partial \beta}$  can both be reduced if stability factor S is x

reduced.

\* Condition for thermal stability or avoiding thermal runaway are

$$\Rightarrow \quad \frac{\partial P_{C}}{\partial T_{j}} < \frac{\partial P_{D}}{\partial T_{j}} \quad (\text{or}) \quad \frac{\partial P_{c}}{\partial T_{j}} < \frac{1}{\theta} \quad (\text{or}) \quad \left[V_{CC} - 2I_{C}(R_{c} + R_{e})\right] \times S \times 0.07I_{CO} < \frac{1}{\theta}$$

where  $\theta$  = thermal resistance.

Best possible of choosing the operating point is  $V_{CE} = \frac{V_{cc}}{2}$ . x

# **GATE AND IES QUESTIONS**

- Introducing a resistor in the emitter of a common emitter amplifier stabilizes the dc operating point against Q.1 variations in

- (a) only the temperature (b) only the  $\beta$

- (c) Both temperature and  $\beta$

- (d) none

### Exp. (c)

R<sub>e</sub> resistor works as a negative feedback which gives stability of the circuit. Therefore it stabilizes against the variation of both temperature and  $\beta$ .

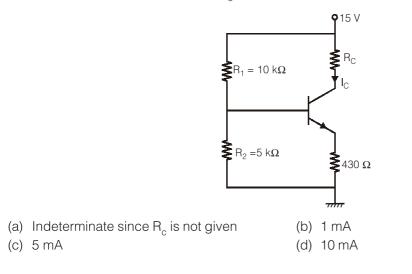

Q.2 In the circuit of the figure, assume that the transistor is in the active region. It has a large  $\beta$  and its baseemitter voltage is 0.7 V. The value of  $\rm I_{\rm c}$  is

### 16 • BJT Biasing and Thermal Stabilization

### Exp. (d)

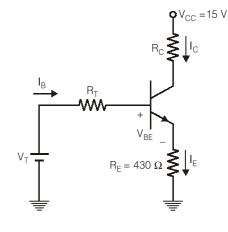

The Thevenin equivalent is shown below:

$$V_{T} = \frac{H_{2}}{R_{1} + R_{2}} V_{cc}$$

$$= \frac{5}{10 + 5} \times 15 = 5 V$$

$I_{C} \approx I_{F}, I_{B} \approx 0$  and

Since  $\beta$  is large

$$I_{E} = \frac{V_{T} - V_{BE}}{R_{E}}$$

$$= \frac{5 - 0.7}{0.430 \,\mathrm{k}\Omega} = \frac{4.3}{0.430 \,\mathrm{k}\Omega} = 10 \,\mathrm{mA}$$

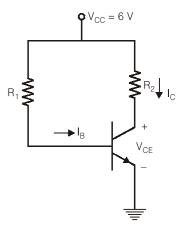

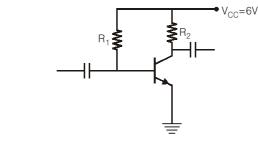

- **Q.3** In the amplifier circuit shown in the figure, the values of  $R_1$  and  $R_2$  are such that the transistor is operating at  $V_{CE} = 3 \text{ V}$  and  $I_C = 1.5 \text{ mA}$ , when its  $\beta$  is 150. For a transistor with  $\beta$  of 200, the operating point ( $V_{CE}$ ,  $I_C$ ) is

- (a) (2 V, 2 mA)

- (b) (3 V, 2 mA)

- (c) (4 V, 2 mA)

- (d) (4 V, 1 mA)

### Exp. (a)

The DC equivalent circuit is shown below: First case:

$$V_{CC} - I_{C_1} R_2 - V_{CE_1} = 0$$

$$6 - 1.5 \text{ mA } R_2 - 3 = 0$$

$$R_2 = 2 \text{ k}\Omega$$

$$I_{B_1} = \frac{I_{C_1}}{\beta_1} = \frac{1.5 \text{ mA}}{150} = 0.01 \text{ mA}$$

### Second case:

$I_{B_2}$  will be equal to  $I_{B_1}$  as there is no change in  $R_1$

$$I_{C_2} = \beta_2 I_{B_2} = 200 \times 0.01 \text{ mA} = 2 \text{ mA}$$

$$V_{CE_2} = V_{CC} - I_{C_2} R_2 = 6 - 2 \text{ mA} \times 2 \text{ k}\Omega$$

$$= 2 \text{ V}$$

### Exp. (d)

For the transistor to be in saturation

$$||_{B} > \frac{|_{C}}{\beta}$$

**Q.31** If for a silicon n-p-n transistor, the base-to-emitter voltage  $(V_{BE})$  is 0.7 V and the collector to base voltage  $(V_{CB})$  is 0.2 V, then the transistor is operating in the

(a) normal active mode

- (c) inverse active mode

- (b) saturation mode

- (d) cutoff mode

Exp. (a)

$\begin{array}{rcl} V_{CE} &=& V_{BE} + V_{CB} \\ &=& 0.7 + 0.2 \\ &=& 0.9 \ V \\ (V_{CE})_{sat} &=& 0.2 \ V \\ Therefore & V_{CE} &>& (V_{CE})_{sat} \\ It is in normal active mode \end{array}$

# **REVIEW QUESTIONS**

- 1. What is the purpose of biasing a transistor? Indicate the methods of biasing and compare them.

- **2.** Define the three different stability factors and give an expression that determine the variation of collector current in terms of stability factor.

- **3.** Explain the effect of temperature on various parameters of a transistor amplifier circuit and discuss the methods of stabilization of the operating point.

- 4. Draw a fixed bias circuit and explain its drawbacks in detail.

- 5. Derive expressions for stability factors of a self bias circuit.

- 6. Explain how stability is improved in a self bias circuit.

- 7. Give a transistor circuit that employs a thermistor to compensate the variation of parameters with temperature and explain the circuit operation.

- **8.** What is a sensistor? Explain how it can be employed in a transistor circuit to compensate the variation of operating point with temperature.

- **9.** Distinguish between stabilization and compensation techniques. Discuss about compensation techniques in detail.

- **10.** What do you understand by thermal run away? Derive the condition for avoiding thermal run-away in a transistor. Explain the term thermal resistance and derive the condition for thermal stability of BJT.